# WORKING OF A THREE PHASE TRANSFORMER MODELING IN DISTRIBUTION POWER SYSTEM

<sup>1</sup>Nayanish V. Ambhore, <sup>2</sup>Shishir S. Pande

<sup>1</sup>Assistant Professor in Electrical Engineering, <sup>2</sup>Assistant Professor in Electrical Engineering, <sup>1</sup>Sanmati Engineering College ,Washim, India

**Abstract**: The purpose of this paper to present that how the three phase transformer is used for different parameters in a distribution of power system. This system are follow the KCl, KVL and on ideal system between primary and secondary side of a transformer. This paper is limited to modeling of Delta-Grounded Wye connection.

#### INTRODUCTION

Presently a days we as a whole know there are increment the interest of power thus numerous individuals are get the vitality from the sustainable power sources, for example, sun powered and the breeze. The appearance period of intensity age from these sources are broadly acknowledged [1]. They are basically boundless and naturally well disposed. Among the other sustainable power sources conceivable to get power, sun oriented vitality has been a standout amongst the most dynamic research territories in the past decennary, both for network associated and remain solitary applications. The fast change rate of development in the overall expanding PV limit is for the most part because of increment in framework associated inverter topologies. Air conditioning yield voltage is made by exchanging the full extension in a proper grouping. The inverter topologies can be isolated into two sorts that are the single and multi-arrange inverter. The staggered inverters are connected in high voltage PV control plant basically because of the high voltage ability, low exchanging recurrence, and low power misfortunes the staggered topologies incorporate the diode clasped, flying capacitor, and fell H-connect converters. The goal of this paper is to exhibit the demonstrating and investigation of a novel seven-level inverter for PV and wind control plant application [2]-[3]. STATCOMs and dynamic voltage controllers (DVRs) have assumed an unequivocal job in improving the blame ride through (FRT) ability of appropriated age frameworks, as showed in. In like manner, propelled control functionalities for the power converters have likewise been proposed, Regardless, a quick recognition of the blame adds to improving the impacts of these arrangements; in this manner, the synchronization calculations are vital. This pattern has been trailed by the remainder of the TSOs; in addition, it is trusted that this task prerequisite will be expanded, and explicit requests for adjusted and uneven hangs will emerge in the accompanying variants of the matrix codes around the world.

## 1. SOLAR RELATED WORK

For the assessment of lattice synchronization topology, the structure is appeared for the basic execution of this technique, considering the necessities that can be gotten from the LVRT requirements. In this the blame are recognize with the assistance of basic calculation, the significance of cutting edge network synchronization frameworks gives the precise data about the extent and period of the matrix voltage amid the blame, so as to infuse the receptive power required by the TSO.

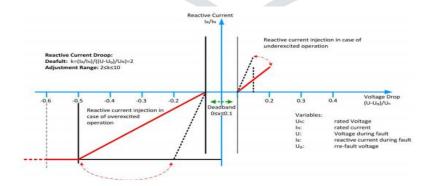

Fig.1 E-on voltage support requirement event of grid fault

A similar condition is given in the Spanish grid code, where the wind power plants are required to stop drawing inductive reactive power within 100 Ms of a voltage drop and be able to inject full reactive power after 150 ms, as shown in Fig.1

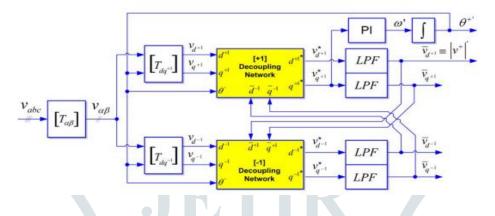

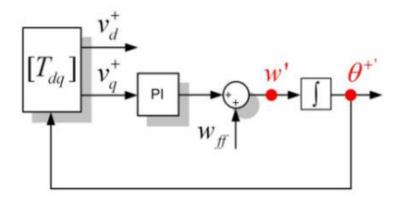

#### 2. DDSRF-PLL

The discovery of the key recurrence positive-arrangement part of the utility voltage under lopsided and contorted conditions. In particular, it proposes a positive-arrangement finder dependent on another decoupled twofold synchronous reference outline stage bolted circle (DDSRF-PLL), which totally kills the recognition mistakes of customary synchronous reference outline PLL's (SRF-PLL). This is accomplished by changing both positive-and negative-arrangement parts of the utility voltage into the twofold SRF, from which a decoupling system is created so as to neatly concentrate and separate the positive-and negative-grouping segments. The resultant DDSRF-PLL leads then to a quick, exact, and hearty positive-succession voltage recognition even under uneven and misshaped lattice conditions.

Fig.2 DDSRF-PLL block diagram

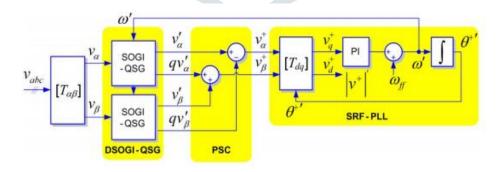

# 3. DSOGI-PLL:

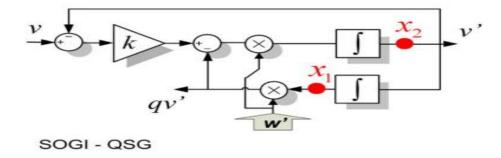

Fig.3 Dsogi-PLL BLOCK DIAGRAM

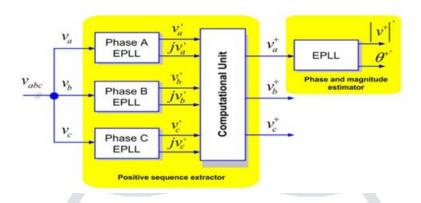

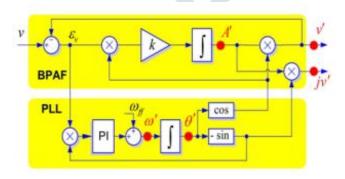

#### 4. PHE-PLL

The upgraded stage bolted circle (EPLL) is a synchronization framework that has demonstrated to give great outcomes in single-stage synchronization frameworks An EPLL is basically a versatile band pass channel, which can change the cut-off recurrence as an element of the info flag. Its structure was later adjusted for the three-stage case, so as to distinguish the positive-grouping vector of three-stage signals, acquiring the 3phEPLL that is spoken to in Fig. 4. For this situation, each stage voltage is handled autonomously by an EPLL

FIG.4 PHE-PLL BLOCK DIAGRAM

#### DISCRETE IMPLEMENTATION

The execution of the diverse structures under test is extremely reliant on their last advanced usage, especially on the discretization approach made to their constant conditions. This usage is basic and ought to be examined in detail as a clear execution can offer ascent to extra deferrals on the up and up that block the great execution of the PLL. A few strategies, for example, the forward Euler, the regressive Euler, and the Tustin (trapezoidal) numerical joining, offer a decent act when utilized for undermining other synchronization frameworks.

## **DDSRF-PLL Discretization**

The discrete model of this PLL can be easily obtained since the continuous representation of several parts does not change in the discrete domain.

## 1) Positive- and Negative-Sequence Decoupling Networks:

The decoupling network constitutes one of the most important contributions of this synchronization method. The discrete equations of these blocks are shown in (1), being almost the same as in the continuous domain. It is just necessary to consider one sample delay of  $\theta$ ,  $v^-d^-1$ ,  $v^-d^-1$ ,  $v^-d^-1$ , and  $v^-q^+1$  in order to avoid algebraic loops.

- 2)Phase and Magnitude Estimator Discretization: In the DDSRF PLL, the decoupling network appears embedded in the classical SRF-PLL loop However, this does not affect the discretization of the phase and magnitude estimator since v\*d+1 and vq\*+1 act as the input of this block.

- 3) LPF Block Discretization: The amplitudes of the dq positive- and negative-sequence components are the outputs of the decoupling networks. However, four infinite impulse responses (IIR) LPFs extract the ripple from each sequence estimation in order to reinforce the performance of the PLL in case of harmonic pollution.

### 5. DSOGI-PLL Discretization

# 1) DSOGI-QSG Block Discretization:

As was recently referenced in Section II, the DSOGI-based quadrature flag generator (QSG) of Fig. 3 comprises of two autonomous and decoupled second-request summed up integrators (SOGIs). Along these lines, each SOGI-based quadrature flag generator can be discredited exclusively, hence encouraging its numerical depiction. In Fig. 5, the square chart of the actualized SOGI is appeared.

Fig.5 Quadrature signal generator based on a second order generalized integrator

FIG.6 State variables of the SRF-PLL block

# 6. 3ph EPLL Discretization

This three-stage framework synchronization framework abuses the EPLL as a quadrature flag generator. A free EPLL is utilized for preparing every last one of the three-stage voltages. The equivalent EPLL structure is connected again to distinguish the extent and period of the positive-arrangement voltage segment

1) QSG Block—EPLL Discretization: The block diagram of the EPLL implemented in this paper

FIG.7 QUADRATURE SIGNAL GENERATOR BASED ON AN EPLL

According to this diagram, the state space representation of the EPLL in the continuous domain can be written as shown in

$$\dot{A}'(t) = k. e(t). \cos \theta'(t)$$

$$\dot{\omega}'(t) = -k. e(t). \sin \theta'(t)$$

$$\theta(t) = \omega'(t) + \frac{k_p}{k_t}. \dot{\omega}'(t)$$

Nonetheless, for the stage and extent recognition hinder, the yields are the positive succession greatness and stage, which relate straightforwardly with the states  $\theta$  and An, individually. In the accompanying segment, the reactions of the DDSRF PLL, DSOGI PLL, and 3PhEPLL under these transient conditions will be thought about.

#### **CONCLUSION**

Conduct of three propelled matrix synchronization frameworks. Their structures have been introduced, and their discrete calculations have been examined.. The DDSRF PLL and the DSOGI PLL permit assessing the ISCs of a three-stage framework working in the αβ reference outline, while the 3phEPLL uses the "abc" reference outline, therefore working with three factors. As has been appeared, rearranges the improves structure of the DSOGI PLL and the DDSRF PLL, which permits diminishing the computational weight, when contrasted with the 3phEPLL, without influencing its execution. The synchronization ability of the three PLLs under test has been appeared to be quick and exact under broken situations, permitting the discovery of the positive arrangement of the voltage in 20–25 ms in all cases; be that as it may, the more straightforward structure of the DDSRF and the DSOGI manages a simpler tuning of their control parameters and, in this manner, a progressively precise control of their transient reaction. The invulnerability of the examined PLLs in the likelihood of a dirtied system is better when utilizing the 3phEPLL and the DDSRF, due to their more prominent band pass and low-pass sifting abilities In spite of the fact that the DSOGI additionally offers ascend to sensibly great outcomes, because of its innate band pass sifting structure, its reaction is increasingly influenced by harmonics. Although every one of the three are fitting for synchronizing with the system voltage in appropriated control age applications, for the most part PV and wind control, the lower computational expense of the DDSRF PLL and the DSOGI PLL, together with their strong estimation of the voltage parameters, offers a superior tradeoff between the exhibited frameworks, making them especially reasonable for wind control application

- A) After doing the literature survey it has been concluded that,

- 1) The behavior of three advanced grid synchronization systems.

- 2) The synchronization capability of the three PLLs under test has been shown to be fast and accurate under faulty scenarios

- B) After modeling grid voltage synchronization for distributed generated system under grid fault condition

- 1) The immunity of the analyzed PLLs in the possibility of a polluted network is better when using the 3phEPLL and the DDSRF.

- 2) Although all three have been shown to be appropriate for synchronizing with the network voltage in distributed power generation applications.

## REFERENCES

[1] S. Jazebi and F. de León, "Tentatively approved reversible singephase mutli-winding transformer display for the precise

count of low-recurrence drifters," IEEE Trans. Power Del., vol. 30, no. 1, pp.193-201, Feb. 2015.

[2] "DCG-EMTP (Development coordination gathering of EMTP) Version EMTP-RV, Electromagnetic Transients Program,"

[Online]. Accessible: http://www.emtp.com

[3] S. Jazebi, S. E. Zirka, M. Lambert, A. Rezaei-Zare, N. Chiesa, Y. Moroz, X. Chen, M. Martinez-Duro, C. M. Arturi, E. P.

Dick, A. Narang, R. A. Walling, J. Mahseredjian, J. A. Martinez, and F. de León, "Duality Derived Transformer Models for

Low-Frequency Electromagnetic Transients – Part I: Topological Models," IEEE Trans. Power Del., Early Access. [4]S. E. Zirka, Y. I. Moroz, N. Chiesa, R. G. Harrison, and H. Kr. Hoidalen, "Execution of backwards hysteresis display into

EMTP – Part II: dynamic model," IEEE Trans. Power Del., Early Access. [27] S. E. Zirka, Y. I. Moroz, and C. M. Arturi, "Representing the impact of the tank dividers in the zero-arrangement topological model of a threephase, three-appendage

transformer," IEEE Trans. Power Del., vol. 29, no. 5, pp. 2172–2179, Oct. 2014. M. Tsili and S. Papathanassiou, "A survey

of network code specialized prerequisites for wind ranches," IET Renew. Power Gen., vol. 3, no. 3, pp. 308–332, Sep. 2009.

[5] F. Iov, A. Hansen, P. Sorensen, and N. Cutululis, "Mapping of Grid Faults and Grid Codes," Risø Nat. Lab., Roskilde,

Denmark, Tech. Rep. RisoeR-1617, 2007.

- [6] A. Luna, P. Rodriguez, R. Teodorescu, and F. Blaabjerg, "Low voltage ride through

- [7] strategies for SCIG wind turbines in dispersed power age frameworks," in Proc. IEEE PESC, Jun. 15–19, 2008, no. 1, pp. 2333–23.